Logický člen

Logický člen neboli hradlo[1] je základní stavební prvek logických obvodů, který vyčísluje logickou funkci. Typicky má jeden či více vstupů a jediný výstup. Hodnota na výstupu logického členu je funkcí hodnot vstupních:

Terminologie

Někdy se pojmy logický člen a hradlo rozlišují. Pojem hradlo pak označuje fyzickou součástku (např. integrovaný obvod), zatímco pod pojmem logický člen je myšlen prvek realizující logickou funkci.

Značení

Existují dva způsoby značení logických členů (oba definované ANSI/IEEE Std 91-1984 a jeho dodatkem ANSI/IEEE Std 91a-1991). Prvním jsou obdélníkové (čtvercové) značky (IEC, DIN). Druhým způsobem jsou značky složené z křivek (ANSI), které jsou rozšířeny v profesionálních systémech pro návrh logických obvodů. U obou způsobů značení existují v praxi drobné varianty. Negovaný výstup je často označen kolečkem.

Základní logické členy

Pomocí logických členů AND, OR a NOT lze realizovat libovolný logický obvod, a tedy i číslicový systém. Členy AND a OR jsou za pomoci členu NOT komplementární. To znamená, že je možné je vhodným způsobem vzájemně nahradit. Lze implementovat jakýkoliv číslicový systém pouze za pomoci logických členů NAND nebo NOR nebo AND a NOT anebo OR a NOT (vždy stačí členy se dvěma vstupy), nikoli však například pomocí členu XOR. NAND a NOR se nazývají univerzální logické členy.

Symboly logických členů

Následuje seznam nejdůležitějších logických členů včetně rovnice v Booleově algebře.

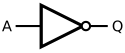

Opakovač (repeater)

Nejjednodušším logickým členem je opakovač, který realizuje funkci identity. Může pracovat i jako buffer - zpožďovací člen s velmi krátkým zpožděním, typicky ns (nanosekundy), oddělovací člen s otevřeným kolektorem, výkonový budič (například sběrnice).

| Funkce | ||

|---|---|---|

| Výraz v C | bool y = a; | |

| Značení | Pravdivostní tabulka | |

| norma | symbol | |

| ANSI/MIL | ||

| IEC | ||

| DIN |  | |

NOT (Invertor)

Dalším nejjednodušším logickým členem je invertor. Realizuje funkci tzv. logické negace. Někdy se místo něj používá negovaného logického součtu s přivedením hodnoty pouze na jediný vstup (v tomto případě "A"). Vzhledem k tomu, že na zbylém anebo zbylých vstupech bude logická 0, nebude mít tento vstup již na provedení operace vliv. Taktéž je možno použít negovaného logického součinu, kdy se všechny vstupy propojí paralelně (mezi sebou).

| Funkce | ||

|---|---|---|

| Výraz v C | bool y = !a; | |

| Značení | Pravdivostní tabulka | |

| norma | symbol | |

| ANSI/MIL | ||

| IEC | ||

| DIN |  | |

AND (Konjunktor)

Tento člen provádí funkci tzv. logického součinu (konjunkce).

| Funkce | ||

|---|---|---|

| Výraz v C | bool y = a && b; | |

| Značení | Pravdivostní tabulka | |

| norma | symbol | |

| ANSI/MIL | ||

| IEC | ||

| DIN |  | |

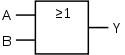

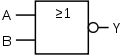

OR (Disjunktor)

Tento člen provádí funkci tzv. logického součtu (disjunkce).

| Funkce | ||

|---|---|---|

| Výraz v C | bool y = a || b; | |

| Značení | Pravdivostní tabulka | |

| norma | symbol | |

| ANSI/MIL | ||

| IEC | ||

| DIN |  | |

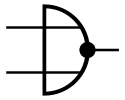

NAND (Shefferova funkce)

Tento člen provádí funkci tzv. negovaného logického součinu (Shefferovu funkci) neboli součet negací. Je to nejběžněji používané hradlo. Propojením vstupů je schopno pracovat jako invertor. Lze pomocí něj realizovat většinu klopných obvodů.

| Funkce | ||

|---|---|---|

| Výraz v C | bool y = !(a && b);

| |

| Značení | Pravdivostní tabulka | |

| norma | symbol | |

| ANSI/MIL | ||

| IEC | ||

| DIN |  | |

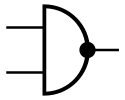

NOR (Peirceova funkce)

Tento člen provádí funkci tzv. negovaného logického součtu (Peirceovu funkci) neboli součin negací. Propojením vstupů je schopen pracovat jako invertor.

| Funkce | ||

|---|---|---|

| Výraz v C | bool y = !(a || b);

| |

| Značení | Pravdivostní tabulka | |

| norma | symbol | |

| ANSI/MIL | ||

| IEC | ||

| DIN |  | |

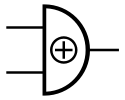

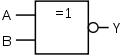

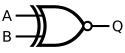

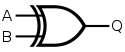

XOR

Tento logický člen vyčísluje exkluzivní logický součet.

| Funkce | ||

|---|---|---|

| Výraz v C | bool y = a ^ b;

| |

| Značení | Pravdivostní tabulka | |

| norma | symbol | |

| ANSI/MIL | ||

| IEC | ||

| DIN |  | |

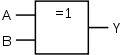

XNOR

Jedná se o negaci exkluzivního logického součtu.

| Funkce | ||

|---|---|---|

| Výraz v C | bool y = !(a ^ b);

| |

| Značení | Pravdivostní tabulka | |

| norma | symbol | |

| ANSI/MIL | ||

| IEC | ||

| DIN |  | |

Realizace

HW realizace

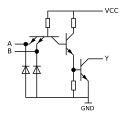

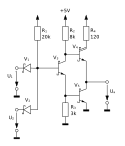

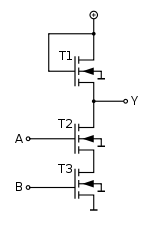

Logický člen je možno realizovat vhodným zapojením aktivních součástek, tranzistorů, dále pak diod, rezistorů či dalších pasivních součástek. Často se lze setkat s logickými členy ve formě integrovaných obvodů (například řady 74xx), v nichž jsou hradla sestavena z několika tranzistorů. Logické integrované obvody se dělí na TTL, SCHOTTKY STTL, SCHOTTKY ALS, HTL, DTL, LS, CMOS, NMOS a další podle technologie výroby.

| Různá provedení hradla NAND | ||

|---|---|---|

|  |  |

| TTL | TTL LS | TTL s otevřeným kolektorem |

|  |  |

| CMOS | NMOS | DTL |

Dnes se samostatné logické členy používají velmi málo a nahrazují je logické obvody s vyšší integrací, které provádějí složitější logické funkce. Tyto funkce jsou ale stále realizovány z mnoha jednodušších obvodů. Dalšími možnostmi realizace mohou být např. relé, hydraulické ventily či elektronky.

SW realizace

V oblasti řízení se logické členy používají pro návrh logických sítí, které se potom aplikují do programovatelných logických automatů. Logické členy jsou potom pouze virtuální a realizaci zvolené logické funkce zajišťuje programový algoritmus.

Odkazy

Reference

- ↑ V počítači jsou jen jedničky a nuly, root.cz

Literatura

- HÁJEK, J.: 2× ČASOVAČ 555: praktická zapojení, nakladatelství BEN - technická literatura, ISBN 80-86056-27-9.

- MALINA, V.: Digitální technika, nakladatelství KOPP, ISBN 80-85828-70-7

- Mašláň, M., D. Žák : Logické obvody I., PřF UP Olomouc, 1993

- Doc. Ing. Jiří Bayer, CSc; Dr.Ing. Zdeněk Hanzálek; Ing. Richard Šusta: Logické systémy pro řízení, Vydavatelství ČVUT, Fakulta elektrotechnická, Praha, 2000, ISBN 80-01-02147-5

Související články

- Logická operace

- Booleova logika

- Třístavová logika

- Binární sčítačka

- NE555

- Zapojení s operačním zesilovačem#Schmittův klopný obvod

- Multivibrátor

- TTL (logika)

- CMOS

Externí odkazy

Obrázky, zvuky či videa k tématu Logický člen na Wikimedia Commons

Obrázky, zvuky či videa k tématu Logický člen na Wikimedia Commons - Elektrické parametry logických obvodů, kombinační logické obvody, elektro.fs.cvut.cz

- Logic Lab, interaktivní online stavebnice

Média použitá na této stránce

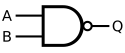

logic AND gate

Autor: Audrius Meskauskas, Licence: CC BY-SA 3.0

The view and element placement of the popular chip 7400. The chip contains four logical elements AND-NOT (NAND). The two additional contacts supply power (+5 V) and connect the ground. This chip was made in the 45th week of 1976.

DIN Symbol for an XOR Gate

logic NAND gate

logic OR gate

DIN Symbol for an XOR Gate

logic XNOR gate

logic BUF gate

A labelled MIL/ANSI symbol for an XNOR gate. A and B are the inputs, Q is the output

DIN Symbol for an NAND Gate

A labelled MIL/ANSI symbol for an AND gate. A and B are the inputs, Q is the output

DIN Symbol for a Buffer

DIN Symbol for an OR Gate

DIN Symbol for a NOR Gate

nand gate

A labelled MIL/ANSI symbol for an OR gate. A and B are the inputs, Q is the output

DIN Symbol for an AND Gate

logic NOT gate

A labelled MIL/ANSI symbol for an XOR gate. A and B are the inputs, Q is the output

Autor: 30px MovGP0, Licence: CC BY 2.0 de

Standard TTL NAND with a "totem-pole" output stage, one of four in 7400.

A labelled MIL/ANSI symbol for an NOR gate. A and B are the inputs, Q is the output

logic XOR gate

A labelled MIL/ANSI symbol for an NAND gate. A and B are the inputs, Q is the output