CMOS

CMOS (anglicky Complementary Metal–Oxide–Semiconductor) je způsob vytváření logických členů vynalezený v 60. letech 20. století a zároveň technologie, kterou se po roce 1985 vyrábí naprostá většina logických integrovaných obvodů, včetně mikroprocesorů, jednočipových počítačů a elektronických pamětí, ale také analogových obvodů, jako jsou snímače obrazu, datové konvertory, zesilovače a transceivery používané v telekomunikacích.

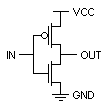

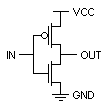

Nejdůležitějšími vlastnostmi obvodů CMOS je nízká spotřeba a vysoká odolnost proti šumu. Z každého páru tranzistorů MOSFET, z nichž je složeno hradlo, je vždy jeden v nevodivém stavu, proto mají obvody CMOS ve statickém stavu mnohem nižší spotřebu energie než obvody NMOS nebo TTL a produkují mnohem méně odpadního tepla; více energie se spotřebovává pouze při přepínání mezi zapnutým a vypnutým stavem tranzistorů. Velmi jednoduchá struktura logických členů a absence rezistorů umožňuje dosažení vysoké hustoty prvků na čipu. Hlavní nevýhodu – nízkou rychlost prvních řad obvodů CMOS – se podařilo odstranit díky miniaturizaci a vylepšené technologii výroby.

Výraz komplementární (complementary nebo někdy complementary-symetric) vyjadřuje, že logické členy jsou vytvářeny dvojicemi doplňujících se tranzistorů MOSFET typu n a p. Zbytek zkratky „metal-oxid-semiconductor“ odkazuje na způsob realizace řídicí elektrody tvořené u prvních obvodů hliníkem odizolovaném tenkou vrstvou oxidu křemičitého od vodivého kanálu z polovodiče. Zkratky MOS a CMOS se používaly, i když se dlouhou dobu – až do 65nm technologie – používal na řídicí elektrody jiný materiál, polykrystalický křemík. Po roce 2010 od technologie 45nm se podle oznámení firem IBM a Intel kovové elektrody s high-k dielektriky opět používají.

Historie

CMOS obvody byly vynalezeny roku 1963 a patentovány roku 1967 (patent 3,356,858) Frankem Wanlassem ze společnosti Fairchild Semiconductor. První integrované obvody byly vyrobeny roku 1968 v RCA pod vedením Alberta Medwina.

Původně byl pro řídicí elektrodu používán hliník, později byl nahrazen polykrystalickým křemíkem, který je odolnější proti vysokým teplotám.

Proces výroby

Proces výroby CMOS obvodů je znázorněn na obrázku vpravo:

- Pokrytí desky vyříznuté z monokrystalu křemíku silnou vrstvou oxidu křemičitého

- Vyleptání oxidu pro vytvoření P-MOSFET

- Vytvoření N-studny (vany)

- Vyleptání oxidu pro vytvoření N-MOSFET

- Pokrytí desky tenkou vrstvou oxidu křemičitého pro vytvoření izolace pod řídicími elektrodami (G – gate)

- Uložení silně dotovaného polykrystalického křemíku tvořícího elektrody G

- Vyleptání oxidu a polykrystalického křemíku

- Vytvoření oblastí pro elektrody S a D difúzním dotováním základního materiálu

- Pokrytí nitridem křemičitým

- Vyleptání nitridu

- Pokrytí kovem pro vytvoření elektrod a jejich propojení

- Vyleptání kovu

Generace podle velikosti

Jednotlivé generace technologie CMOS se označují jedním číslem představujícím šířku hradla tranzistorů na čipu. Minimální velikost hradla je nižší, naopak vlnová délka světla použitého při procesu může být díky různým efektům vyšší.

Čím menší velikost, tím nižší je možné používat napětí (čímž se snižuje spotřeba) a tím je možné dosáhnout vyšších frekvencí.

- 10 µm

- 3 µm

- 1.5 µm

- 1 µm

- 800 nm (0,80 µm)

- 3 µm

- Používá se například na Intel 80486.

- 600 nm (0,60 µm)

- 350 nm (0,35 µm)

- 250 nm (0,25 µm)

- 180 nm (0,18 µm)

- 350 nm (0,35 µm)

- První technologie „menší“ než vlnová délka použitého světla (193 nm).

- Používalo se například na většinu Intel Pentium III.

- 130 nm (0,13 µm)

- Rok 2002; použito pro Intel Pentium IV (55 miliónů tranzistorů, 1,6 GHz, min. 1,5 V)

- 90 nm

- Rok 2003 (min. 1,2 V)

- 65 nm

- Min. 0,9 V; V roce 2007 nejčastěji používaná technologie. Používalo se světlo vlnových délek 193 nm a 248 nm. Šířka elektrody je pouhých 1,2 nm, což je jen několik atomů – dochází tedy k tunelovému jevu.

- Použito například na Intel Pentium IV nebo AMD Athlon 64.

- 45 nm

- Rok 2011; min. 0,6 V; 3 GHz

- 32 nm

- Použito například na Intel Core 2. generace Sandy Bridge.

- 22 nm

- Použito například na Intel Core 3. generace Ivy Bridge.

- 14 nm

- Rok 2014; Intel Core - Broadwell, poté v roce 2015 Skylake a v roce 2017 Kaby Lake

- 7 nm

- Teoretická hranice čistě křemíkových čipů. Pod touto hranicí dochází k manifestaci kvantového tunelování.

- Rok 2018; Apple A12 Bionic, AMD architektura ZEN2

- Rok 2020; AMD architektura ZEN3

- Rok 2018; Apple A12 Bionic, AMD architektura ZEN2

Odkazy

Reference

V tomto článku byl použit překlad textu z článku CMOS na anglické Wikipedii.

Literatura

- Jedlička Petr: Přehled obvodů řady CMOS 4000 – 1. díl – řada 4000 až 4099, BEN - technická literatura, 1994-2005, ISBN 80-7300-167-5

- Jedlička Petr: Přehled obvodů řady CMOS 4000 – 2. díl – řada 41xx, 43xx, 45xx, 40xxx, BEN - technická literatura, 1994-2005, ISBN 80-7300-168-3

Související články

Externí odkazy

Obrázky, zvuky či videa k tématu CMOS na Wikimedia Commons

Obrázky, zvuky či videa k tématu CMOS na Wikimedia Commons

Média použitá na této stránce

Autor: unknown, Licence: CC BY-SA 3.0

Simplified process of fabrication of a CMOS inverter on p-type substrate in semiconductor microfabrication. Note: Gate, source and drain contacts are not normally in the same plane in real devices, and the diagram can be scale.