DRAM

DRAM (anglicky Dynamic Random Access Memory) je asynchronní počítačová paměť, která uchovává data v podobě elektrického náboje v kondenzátoru, který odpovídá parazitní kapacitě řídící elektrody (gate) tranzistoru typu MOSFET. Tento tranzistor současně slouží i jako čítací prvek paměťové buňky – bitu.

V praxi byly asynchronní typy DRAM nahrazeny modernějšími synchronními typy SDRAM a DDR SDRAM (a jejich novějšími verzemi DDR2, DDR3, DDR4 a DDR5).

Charakteristiky

- Paměť typu DRAM je destruktivní při čtení. To znamená, že při každém přečtení se data z paměti vymažou. Avšak data se ihned po přečtení uloží do vyrovnávací paměti, odkud se okamžitě zase obnoví. Uživatel tedy samozřejmě o svá data nepřijde.

- I když je paměť připojena ke zdroji elektrického napětí, dochází v každé buňce neustále k pomalému vybíjení náboje. Proto paměť typu DRAM vyžaduje pravidelné obnovení elektrickým proudem, tj. opětovné nabíjení parazitní kapacity tzv. refresh.

- Dynamické paměti se vyznačují šestinásobně větší hustotou zaznamenané informace oproti statickým pamětím SRAM což má za následek nižší cenu při vyšší kapacitě.

- Na rozdíl od SRAM mají kvůli potřebě stálého obnovování nezanedbatelnou spotřebu energie i když se k nim nepřistupuje (nedochází k zápisu ani ke čtení).

- Paměť má ve srovnání s SRAM delší přístupový čas.

- Paměť vykazuje vážnou hardwarovou zranitelnost (umožňuje změnit bity v řádku paměti příliš častou změnou sousedních řádků).[1]

Konstrukce

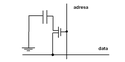

Výhoda DRAM spočívá v její konstrukční jednoduchosti: pouze jeden tranzistor a jeden kondenzátor pro jeden bit, namísto čtyř až šesti tranzistorů u SRAM. To umožňuje DRAM dosáhnout vysoké hustoty. Na rozdíl od flash paměti je DRAM nestálá (volatilní) a ztrácí tak rychle svá data, pokud je odpojena od napájení. Tranzistory a kondenzátory jsou extrémně malé – na jeden paměťový čip se jich vejdou miliardy. DRAM je většinou uspořádána do obdélníkové řady paměťových buněk (matice, šachovnice). Obrázek vpravo ukazuje jednoduchý příklad matice s 4 buňkami na výšku a 4 na šířku, moderní matice jich však mají tisíce.

Čtení a zápis

Čtení

Čtení z paměti neprobíhá tak, že bychom paměti udali adresu a ona vrátila bit, který je na ní uložen. Z technologických důvodů se čtení z paměti skládá ze 2 operací – dílčí čtení a dílčí zápis. Při dílčím čtení se přečte celý řádek paměťové matice a uloží se do vyrovnávací paměti. Při tom dochází k vymazání dat (viz výše). Přečtený řádek se poté obnoví dílčím zápisem, při kterém se informace uloží na své původní místo.

Zápis

I zápis do paměti se skládá ze stejných 2 operací jako čtení. Nejprve se provede dílčí čtení, při kterém se přečte celý řádek paměťové matice a uloží se do vyrovnávací paměti. Poté se ve vyrovnávací paměti změní požadované bity, které se mají do paměti zapsat a následně se při dílčím zápisu celý řádek z vyrovnávací paměti obnoví na původní adresu.

Odkazy

Reference

- ↑ MORSCH, Oliver. Serious security vulnerabilities in DRAM memory devices. TechXplore [online]. 2021-11-16 [cit. 2022-10-04]. Dostupné online. (anglicky)

Externí odkazy

Média použitá na této stránce

Autor: Glogger na projektu Wikipedie v jazyce angličtina, Licence: CC BY-SA 3.0

DRAM ece385 illustrative example. I drew this with idraw for my ECE385 course, to illustrate how DRAM (Dynamic random access memory) works, with simple 4 by 4 array.