Hradlo A20

Hradlo A20 je zvláštní hradlo typu AND na počítačích s procesory 80286 a kompatibilními, kterým je možné nulovat 21. bit na adresní sběrnici těchto procesorů. Bylo zavedeno pro možnost dosažení plné zpětné kompatibility se staršími procesory typu Intel 8086, Intel 8088 a Intel 80186 a nulování bylo standardně možné nastavit nebo vypnout v rozhraní BIOSu. Počínaje architekturou Haswell přestala firma Intel na svých procesorech toto hradlo podporovat.

Princip fungování

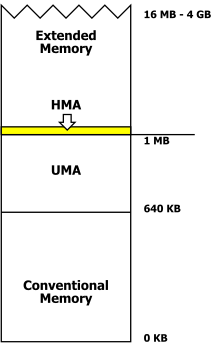

Na prvních procesorech x86 fungujících pouze v reálném režimu byla operační paměť spravována za pomoci segmentace. Logická adresa se skládala ze dvou šestnáctibitových hodnot, segmentu a ofsetu, a převod na fyzickou adresu odpovídal jednoduchému vzorečku segment×16+ofset, což by umožňovalo adresovat až (šestnáctkově zapsáno) 0xFFFF×0x10+FFFF=0x10FFEF bajtů paměti. Protože ale adresní sběrnice těchto procesorů měla jen dvacet bitů (číslovaných od 0 až 19), fyzicky bylo možné adresovat jen 0xFFFFF bajtů (tedy jeden mebibajt). Tento rozpor nebyl u prvních počítačů problémem, protože tolika pamětí nedisponovaly, a problém byl vyřešen tak, že při výpočtu fyzické adresy z logické byl přenos do 21. bitu ignorován a například logická adresa 0xFFFF:0x0010 odpovídala stejně jako logická adresa 0x0000:0x0000 fyzické adrese 0x00000.

Programátoři tuto částečně cyklickou adresaci využívali, dokonce ji využili programátoři operačního systému MS-DOS. Aby zajistili žádoucí kompatibilitu s operačním systémem CP/M, nastavili v prefixu programového segmentu hodnotu ukazatele na obsluhu systémového volání vysokou, byť v MS-DOSu byla cílem fyzická adresa 0x000C0, protože CP/M naopak předpokládal vysokou hodnotu ofsetu. Právě přetečení na prvních procesorech umožnilo adresovat fyzickou adresu 0x000C0 logickou adresou s vysokým ofsetem.

Pozdější procesory 80286 se širší sběrnicí a větším množstvím paměti ale s 21. bitem fyzické adresy počítaly standardním způsobem (a v režimu chráněné virtuální paměti mohly standardně používat násobně více paměti než jeden mebibajt) a to i v reálném režimu, který podporovaly právě pro kompatibilitu se staršími programy. Aby tedy bylo dosaženo plné kompatibility, bylo na základní desku přidáno hradlo k adresnímu vodiči A20, které 21. bit volitelně nulovalo a jehož ovládání bylo připojeno na nevyužívaný výstup řadiče klávesnice (tehdy Intel 8042).

Pro úplnou kompatibilitu byl výchozí stav po spuštění počítače takový, že 21. bit fyzické adresy byl nulován, stejně jako na starších procesorech. Přestože paměťové nároky programů rostly, ještě dlouho po nástupu procesoru 80286 pracovala většina počítačů s operačním systémem MS-DOS v reálném režimu, ve kterém je logická adresa omezena na 0xFFFFF bajtů. Proto bylo běžné nulování 21. bitu vypnout a tím umožnit používání 65520 bajtů takzvané high memory area.

S nástupem počítačů pracujících standardně v chráněném režimu se vypnutí nulování 21. bitu stalo rutinní součástí startu operačního systému, často ještě v jeho zavaděči.

Odkazy

Reference

V tomto článku byl použit překlad textu z článku A20 line na anglické Wikipedii.

Související články

Média použitá na této stránce

Autor: Wtshymanski, Licence: CC BY-SA 3.0

IBM PC memory map showing memory areas