Hradlo OR

Hradlo OR, zkráceně jen OR, je logický člen, který realizuje operaci logické disjunkce. Z pravdivostní tabulky hradla OR vyplývá, že na výstupu hradla bude logická 1, pokud alespoň na jednom ze vstupů hradla bude signál, který odpovídá logické 1.

| Pravdivostní tabulka | ||

|---|---|---|

| Vstupy | Výstup | |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Logika hradla

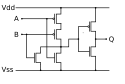

Implementace hradla

|  |  |

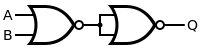

Náhrada hradla OR

Hradlo OR je možné v zapojení elektronického obvodu nahradit pomocí hradel NOR nebo NAND.

| Hradlo OR | OR pomocí obvodů NAND | OR pomocí obvodů NOR |

|---|---|---|

|  |  |

Řada 4000

- 4071: 4× hradlo OR se čtyřmi vstupy [2]

- 4072: 2× hradlo OR se čtyřmi vstupy[3]

- 4075: 3× hradlo OR se třemi vstupy[3]

Řada 7400

- 7432: 4× hradlo OR s dvěma vstupy [4]

Související články

Externí odkazy

Obrázky, zvuky či videa k tématu Hradlo OR na Wikimedia Commons

Obrázky, zvuky či videa k tématu Hradlo OR na Wikimedia Commons

Reference

- ↑ PECINA, Josef; PECINA, Pavel. Základy číslicové techniky [online]. Pedagogická fakulta Masarykovy univerzity, 2007 [cit. 2021-05-01]. Dostupné v archivu pořízeném dne 2021-04-27.

- ↑ Datasheet CD4071BC • CD4081BC [online]. Fairchield Semiconductor, 1987-10, rev. 2002-04 [cit. 2021-05-01]. Dostupné online. (angličtina)

- ↑ a b Datasheet CD4071B, CD4072B, CD4075B [online]. Texas Instruments, rev. 1999 [cit. 2021-05-01]. Dostupné online. (angličtina)

- ↑ Datasheet sn_7432 [online]. Texas Instruments, rev. 1996 [cit. 2021-05-01]. Dostupné online. (angličtina)

Média použitá na této stránce

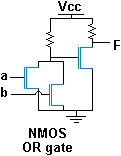

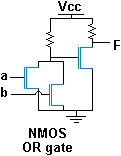

用PMOS構成的或閘。

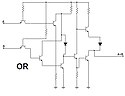

logic OR gate

Layout of NMOS and PMOS components in an OR Gate. This OR gate is implemented as an AND gate with both inputs inverted(by using PMOS at the top) as well as the output (inverter at the right) which is functionally correct, but is not commonly used as it requires 2 extra transistors.

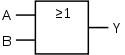

A labelled MIL/ANSI symbol for an OR gate. A and B are the inputs, Q is the output